Obijuan · @Obijuan

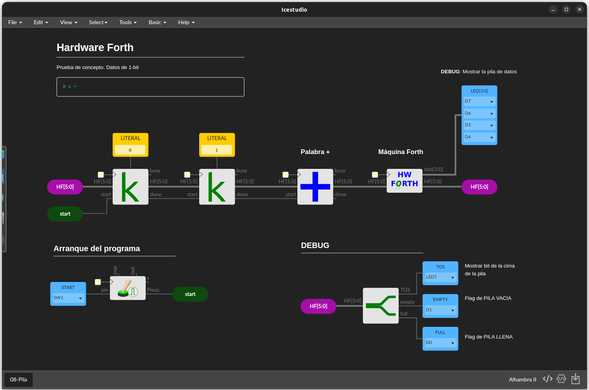

123 followers · 181 posts · Server mstdn.socialque me sirve como prueba de concepto. Y la cosa de momento es viable. Muchísimas gracias a @adumont

. Su proyecto AlexForth es toda una inspiración. He aprendido muchísimo con él. ¡Muchas gracias!

Los circuitos de prueba los estoy dejando temporalmente en este directorio del repositorio de los cuadernos ténicos de FPGAs libres: https://github.com/Obijuan/Cuadernos-tecnicos-FPGAs-libres/tree/master/wiki/Pila #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialLlevo unos días trabajando en una prueba de concepto: Hacer circuitos usando la filosofía del lenguaje FORTH. Las palabras Forth son bloques hardware de #icestudio conectados en serie. Algunos bloques son primitivo: están implementados directamente en hardware #FPGAwars

Obijuan · @Obijuan

122 followers · 154 posts · Server mstdn.socialEn el siguiente nivel (nivel 2) iré bloque por bloque añadiendo iconos y documentación, para entender qué es cada parte. Este nivel 2 todavía dependerá de ficheros verilog externos, pero su top-level será totalmente gráfico #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialEn el siguiente nivel (nivel 2) iré bloque por bloque añadiendo iconos y documentación, para entender qué es cada parte. Este nivel 2 todavía dependerá de ficheros verilog externos, pero su top-level será totalmente gráfico #FPGAwars

Obijuan · @Obijuan

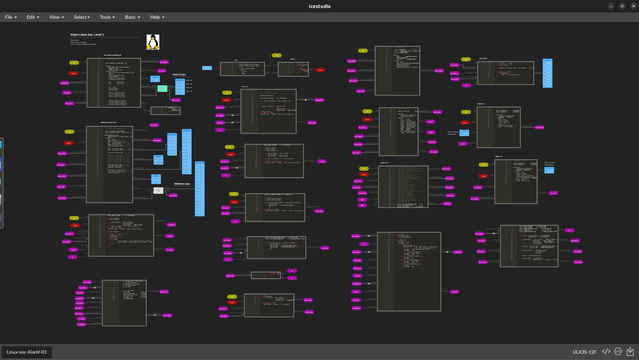

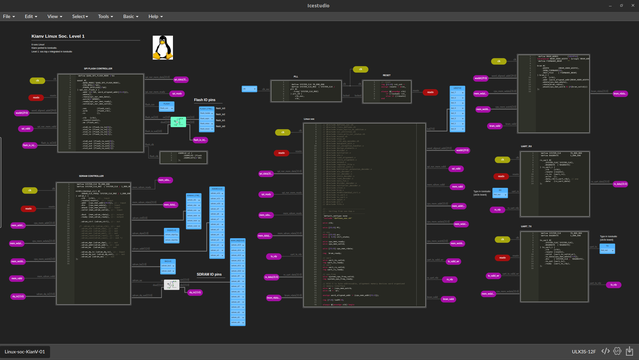

122 followers · 153 posts · Server mstdn.socialYa está terminado el nivel 1. Todo el código verilog del fichero principal soc-top.v se ha distribuido en diferentes bloques de icestudio (con código verilog). El resto de ficheros verilog se tienen que editar externamente a Icestudio, todavía #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialYa está terminado el nivel 1. Todo el código verilog del fichero principal soc-top.v se ha distribuido en diferentes bloques de icestudio (con código verilog). El resto de ficheros verilog se tienen que editar externamente a Icestudio, todavía #FPGAwars

Obijuan · @Obijuan

121 followers · 151 posts · Server mstdn.socialYa tengo separados el controlador de la memoria flash-spi, el de la SDRAM, el circuito de reset y reloj, el transmisor y receptor serie, y la memoria BRAM. En el centro están en verilog el resto de cosas:

controlador de interrupciones, cpu y lógica de selección. Es lo siguiente en lo que voy a trabajar #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialYa tengo separados el controlador de la memoria flash-spi, el de la SDRAM, el circuito de reset y reloj, el transmisor y receptor serie, y la memoria BRAM. En el centro están en verilog el resto de cosas:

controlador de interrupciones, cpu y lógica de selección. Es lo siguiente en lo que voy a trabajar #FPGAwars

Obijuan · @Obijuan

121 followers · 150 posts · Server mstdn.socialEstoy avanzando en el nivel 1. Los componentes del top-level (soc-top.v) se están distribuyendo en diferentes bloques de verilog. Cada bloque de verilog instancia su propio fichero. Lo interesante es que se empiezan a ver sus partes y las conexiones entre ellas #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialEstoy avanzando en el nivel 1. Los componentes del top-level (soc-top.v) se están distribuyendo en diferentes bloques de verilog. Cada bloque de verilog instancia su propio fichero. Lo interesante es que se empiezan a ver sus partes y las conexiones entre ellas #FPGAwars

Obijuan · @Obijuan

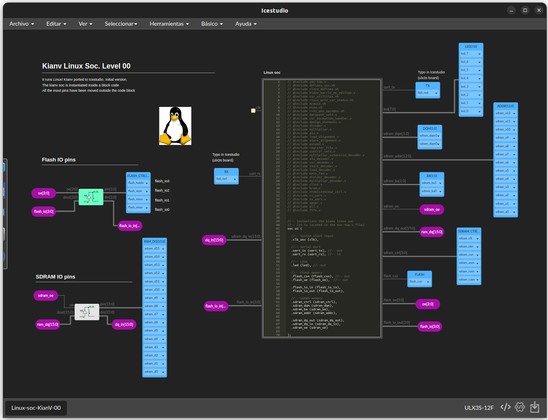

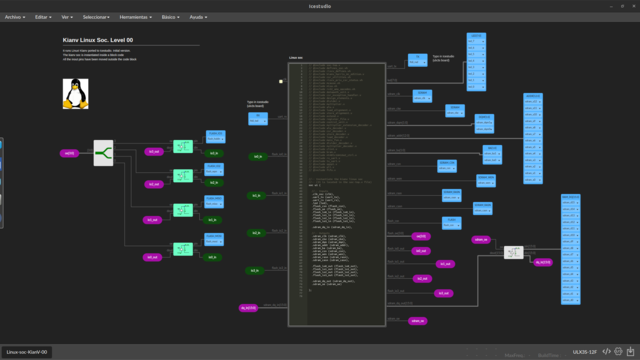

121 followers · 148 posts · Server mstdn.socialEsta es la nueva versión, refactorizada, del nivel 0. En este nivel se respetan los ficheros verilog originales, y se ha añadido un top-level gráfico para que la síntesis sea sencilla. Para añadir o eliminar componentes hay que hacerlo en Verilog #FPGAWars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialEsta es la nueva versión, refactorizada, del nivel 0. En este nivel se respetan los ficheros verilog originales, y se ha añadido un top-level gráfico para que la síntesis sea sencilla. Para añadir o eliminar componentes hay que hacerlo en Verilog #FPGAWars

Obijuan · @Obijuan

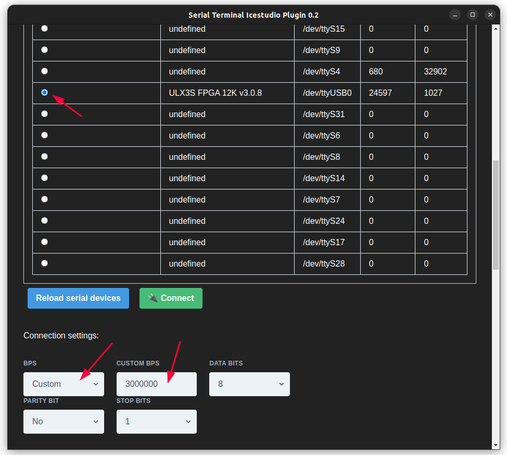

123 followers · 181 posts · Server mstdn.socialTambién se puede probar directamente con el terminal integrado de icestudio (que es multiplataforma), lo que hace más fácil que la gente lo pueda probar en cualquier plataforma (Linux/Mac/Win). Así es como se debe configurar #FPGAwars

Obijuan · @Obijuan

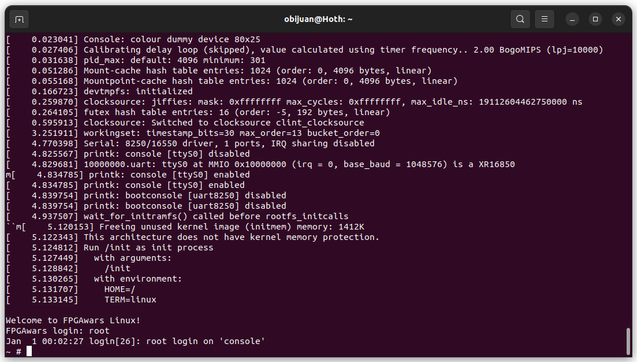

123 followers · 181 posts · Server mstdn.socialUna vez cargado, desde un terminal serie a la verlocidad de 3M baudios, veremos nuestro flamante linux aparecer en la consola 😀 Me sigue pareciendo muy emocionante verlo... #FPGAwars

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialYa tengo una primera versión del KianV Linux Soc migrada a #icestudio La ventaja es que ahora se sintetiza y se carga en la FPGA con un único click de ratón. En este nivel (nivel 0) se usa un bloque verilog para instanciar el modulo soc del fichero soc-top.v #FPGAwars

Obijuan · @Obijuan

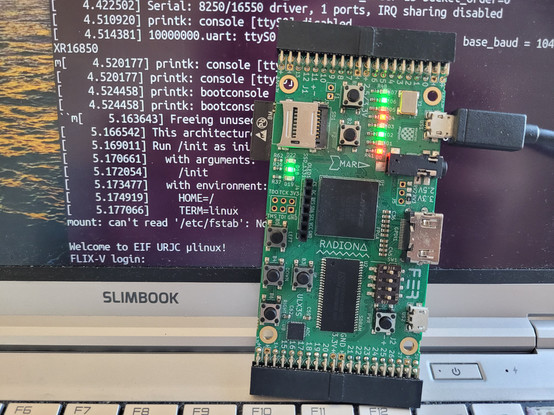

123 followers · 181 posts · Server mstdn.socialEstoy corriendo un linux (sin MMU) en un procesador RISC-V (Kianv) en la FPGA de la placa Hardware abierto ULX3S-12F de @radiona

(Gracias al trabajo de @splinedrive

)

Todos los archivos necesarios están ya compilados para que los pueas probar fácilmente, si quieres... #FPGAwars

Obijuan · @Obijuan

117 followers · 119 posts · Server mstdn.socialObijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialObijuan · @Obijuan

111 followers · 88 posts · Server mstdn.socialThe iceRegs 0.1.0 collection with register for #icestudio has been released

You can find the documentation (In English) in this link:

https://github.com/FPGAwars/iceRegs/wiki

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialThe iceRegs 0.1.0 collection with register for #icestudio has been released

You can find the documentation (In English) in this link:

https://github.com/FPGAwars/iceRegs/wiki