Bruno Levy · @BrunoLevy01

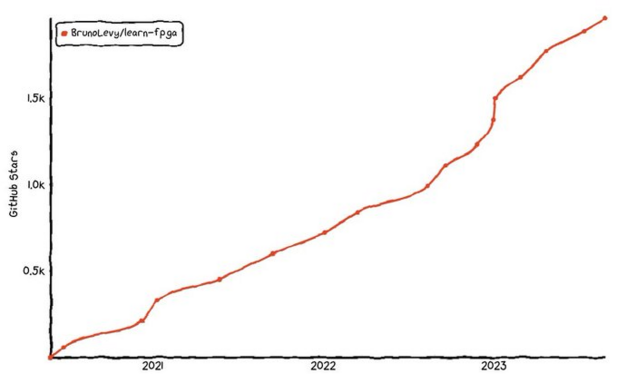

537 followers · 409 posts · Server fosstodon.orglearn-fpga, the tutorial to create @risc_v

cores such as #femtorv on #fpga is approaching 2K stars on github !

https://github.com/BrunoLevy/learn-fpga

Bruno Levy · @BrunoLevy01

497 followers · 383 posts · Server fosstodon.orgBruno Levy · @BrunoLevy01

471 followers · 363 posts · Server fosstodon.orgTomorrow, @risc_v

meeting at Inria Paris. I will be talking about the learn-fpga project (https://github.com/BrunoLevy/learn-fpga). Everyone can design his own RISC-V softcore on a FPGA, it is easy ! (no more than 200 lines of VERILOG for #femtorv)

Bruno Levy · @BrunoLevy01

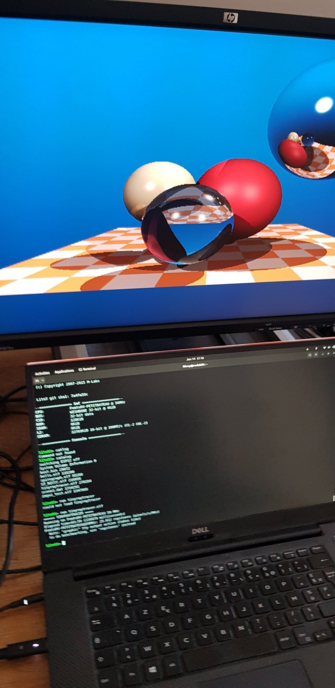

467 followers · 361 posts · Server fosstodon.org#RISCV softcore #femtorv on #FPGA, using the LiteX system: design your own processor, plug-in SDRAM, framebuffer, SDCard, write some programs.

https://github.com/BrunoLevy/learn-fpga/blob/master/LiteX/README.md

Bruno Levy · @BrunoLevy01

452 followers · 342 posts · Server fosstodon.orgPort of the 90's ST_NICCC demo (https://www.pouet.net/prod.php?which=1251), running on #femtorv risc-v core

(https://github.com/BrunoLevy/learn-fpga)

Bruno Levy · @BrunoLevy01

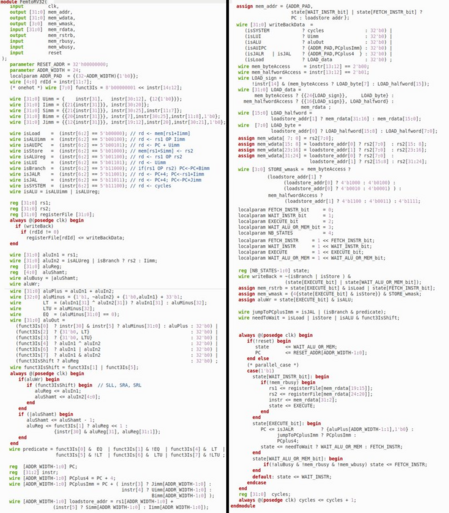

419 followers · 316 posts · Server fosstodon.org43/N

If you installed Yosys/NextPNR, generated a bitstream, made the little LEDs blink, then you are not that far away from a fully functional microprocessor. Am I joking ? Let me show you: this image is the complete VERILOG for #femtorv (200 lines).

Bruno Levy · @BrunoLevy01

395 followers · 260 posts · Server fosstodon.orgCould be a great starting point for writing #femtorv episodes 3 (Zicsr) and episode 4 (virtual memory) for a full gentle continuous path from blinker to Unix-capable CPU.

Episodes 1 (minimalistic CPU) and 2 (pipelining) are here:

https://github.com/BrunoLevy/learn-fpga/blob/master/FemtoRV/TUTORIALS/FROM_BLINKER_TO_RISCV/README.md

Help needed !

Bruno Levy · @BrunoLevy01

395 followers · 259 posts · Server fosstodon.orgAmazing project by Michael Schröder: minimalistic Unix-like system on a minimalistic processor, in the spirit of #femtorv (but with interrupts and virtual memory !)

https://gitlab.com/x653/xv6-riscv-fpga

... and last but not least, it comes with a 3D-printable case with NeXT vibes, love it !

Bruno Levy · @BrunoLevy01

295 followers · 89 posts · Server fosstodon.orgBruno Levy · @BrunoLevy01

166 followers · 35 posts · Server fosstodon.orgFor more fun, you can add a $2 led matrix + MAX7219, and generate additional hardware to drive it. Then your #femtorv processor can say hello to you !