Michael J. Brodeur · @MichaelJBrodeur

57 followers · 3434 posts · Server fosstodon.org@BrunoLevy01 I have several #FPGA boards here. Three of them have an #ICE40 FPGA, three of them are Xilinx-based, and the last is the #ECP5 evaluation board with an ECP5-5G 85F. Which do you recommend for your FPGA tutorial series? Thank you!

Computer Engineering JMU · @ce

6 followers · 7 posts · Server mastodon.acm.org@phf @yosyshq this is the upduino v1 board with #Lattice #ice40 (there is even a v3) HW Description (mainly a I2C controller) is done in #GHDL and synthesis with #yosys and it’s ghdl plugin. Place and route is done with #nextpnr. Picture shows #FPGA floorplan and utilization.

#lattice #ice40 #ghdl #yosys #nextpnr #fpga

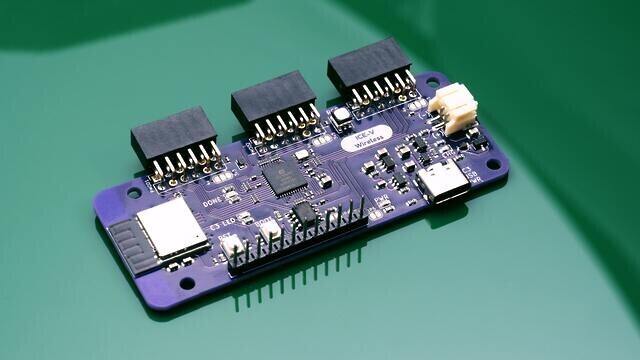

OSH Park · @oshpark

1413 followers · 136 posts · Server fosstodon.orgAnother round of ICE-V Wireless boards by @m_w is now being offered. The design combines the ICE40UP5K FPGA with a wireless interface driven by ESP32-C3 https://groupgets.com/campaigns/1203 #fpga #ice40 #openhardware #esp32 #riscv #oshw #kicad

#fpga #ice40 #openhardware #esp32 #riscv #oshw #kicad

Kristoff (ON1ARF) · @on1arf

63 followers · 58 posts · Server mastodon.radioSome years ago, I bought an #olimex #ice40 8K #fpga board, and 100 MHz ADC and DAC addon boards (*). I have never really used them.

Now I want try to use them to experiment with #sdr with fpga.

Anybody any good references on "getting started with SDR with FPGAs" ?

I guess I should start with a basic DDS circuit?

BTW. I'm on ubuntu so development will be with the open-source rool.

Kevin Webb · @kvnweb

501 followers · 128 posts · Server hachyderm.ioJust discovered a #rustlang path to #FPGA HDL development that's really fun, and feels like a bit of breakthrough in terms of ergonomics:

https://docs.rs/rust-hdl/latest/rust_hdl/

It uses rustc to validate the design using a subset of the Rust language, and builds integrated Rust-based tests that link to internal simulations. It went from .rs to .v to programming a device (#ice40 via apio) from the command line with ease...

Sahaj Sarup · @ric96

162 followers · 1411 posts · Server mastodon.onlineRT @machdyne@twitter.com

The Eis #FPGA computer is now available. 🍨 #RISCV #ICE40 #RP2040 https://machdyne.com/product/eis-computer/