Obijuan · @Obijuan

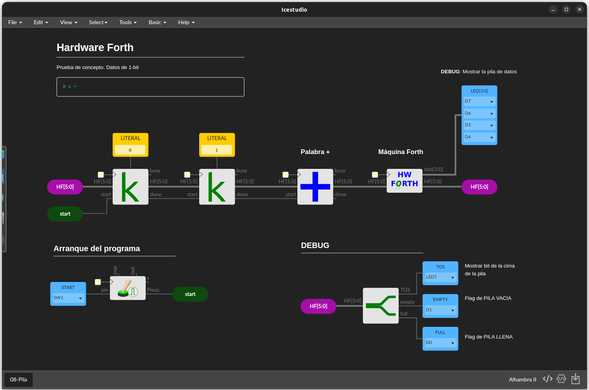

123 followers · 181 posts · Server mstdn.socialLlevo unos días trabajando en una prueba de concepto: Hacer circuitos usando la filosofía del lenguaje FORTH. Las palabras Forth son bloques hardware de #icestudio conectados en serie. Algunos bloques son primitivo: están implementados directamente en hardware #FPGAwars

Obijuan · @Obijuan

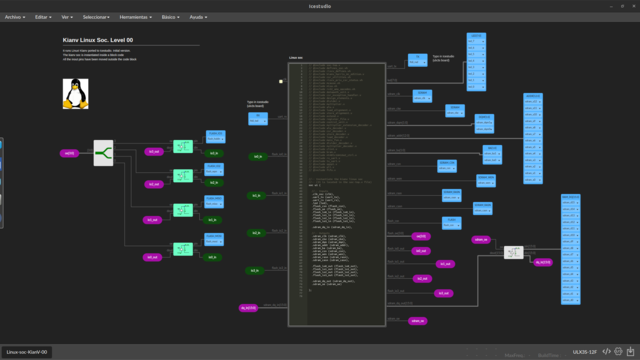

123 followers · 181 posts · Server mstdn.socialTenerlo en #icestudio es genial para hacer talleres y demos rápidas a los estudiantes. Esta primera versión está disponible en este repo: https://github.com/FPGAwars/FLIX-V/tree/main/Hardware/KianV-Icestudio/Level-00

Ahora me centraré en simplificarlo e ir poco a poco conviertiendo el verilog en módulos icestudio

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialYa tengo una primera versión del KianV Linux Soc migrada a #icestudio La ventaja es que ahora se sintetiza y se carga en la FPGA con un único click de ratón. En este nivel (nivel 0) se usa un bloque verilog para instanciar el modulo soc del fichero soc-top.v #FPGAwars

Obijuan · @Obijuan

111 followers · 88 posts · Server mstdn.socialThe iceRegs 0.1.0 collection with register for #icestudio has been released

You can find the documentation (In English) in this link:

https://github.com/FPGAwars/iceRegs/wiki

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialThe iceRegs 0.1.0 collection with register for #icestudio has been released

You can find the documentation (In English) in this link:

https://github.com/FPGAwars/iceRegs/wiki

Obijuan · @Obijuan

111 followers · 87 posts · Server mstdn.socialLiberada la colección iceRegs v0.1.0 con registros para #icestudio. La documentación (en Inglés) está disponible aquí:

https://github.com/FPGAwars/iceRegs/wiki

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialLiberada la colección iceRegs v0.1.0 con registros para #icestudio. La documentación (en Inglés) está disponible aquí:

https://github.com/FPGAwars/iceRegs/wiki

IT News · @itnewsbot

2861 followers · 248746 posts · Server schleuss.onlineCreate Your RTL Simulations With KiCAD - [Bob Alexander] is in the process of designing a homebrew discrete TTL CPU, and wa... - https://hackaday.com/2023/02/06/create-your-rtl-simulations-with-kicad/ #softwarehacks #simulation #icestudio #verilog #kicad #rtl

#rtl #kicad #verilog #icestudio #simulation #softwarehacks

GeekProjects News · @news

1 followers · 2084 posts · Server geekprojects.comCreate Your RTL Simulations With KiCAD https://hackaday.com/2023/02/06/create-your-rtl-simulations-with-kicad/ #SoftwareHacks #simulation #icestudio #verilog #KiCAD #RTL

#SoftwareHacks #simulation #icestudio #verilog #kicad #RTL

Obijuan · @Obijuan

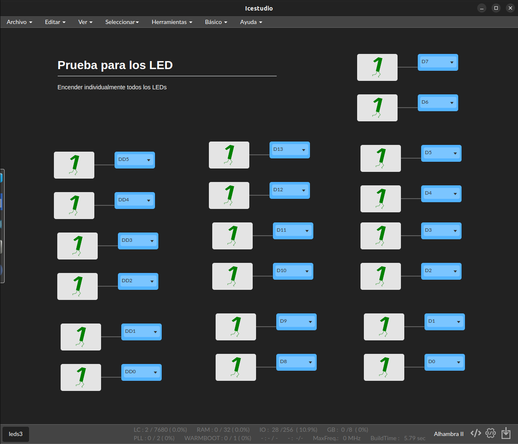

104 followers · 73 posts · Server mstdn.socialEste es el circuito en #icestudio cargado en la #FPGA. Se ponen todas las salidas a 1, individualmente

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialEste es el circuito en #icestudio cargado en la #FPGA. Se ponen todas las salidas a 1, individualmente

Obijuan · @Obijuan

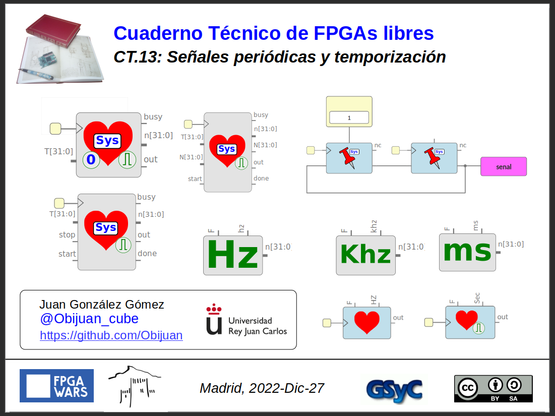

96 followers · 44 posts · Server mstdn.socialPublicado el cuaderno técnico 13 de FPGAs Libres: Señales periódicas y temporización #FPGAwars #icestudio

Obijuan · @Obijuan

123 followers · 181 posts · Server mstdn.socialPublicado el cuaderno técnico 13 de FPGAs Libres: Señales periódicas y temporización #FPGAwars #icestudio

David R :antiverified: · @davidr

192 followers · 1403 posts · Server hachyderm.io@remi Welp, that didn't take long

Got to a project that seems like you'd want like...arrays and busses and stuff. But #icestudio has nothing like that

Looked up some verilog spex and there's a LOT that's missing

Googling found this super-helpful and simple open-source toolchain:

I don't know if things have gotten easier in the last 10 years or if the proprietary world is garbage or if the #nandland #fpga guy is just a glutton for punishment, but this is way easier

David R :antiverified: · @davidr

192 followers · 1403 posts · Server hachyderm.io@remi I think I will probably go to full source based at least bc that's just how I roll. Plus the collections of blocks available is pretty sparse.

The simple GUI is helping me a lot understanding how things *should* work, though. #icestudio seems to report out the full commands it is running behind the scenes, so maybe I can set up a #Makefile or script or whatever.

kudos from a pro is reassuring indeed! thanks!

David R :antiverified: · @davidr

187 followers · 1384 posts · Server hachyderm.ioI'm really impressed with the #opensource #icestudio #fpga programmer so far. And I usually *hate* #guis.

The workflow in the #nandland #goboard tutorials looks so extremely painful compared to this.

I'm definitely still bracing for "my" way to turn out harder/worse in the long run, tho.

The top row is basically a direct copy of the tutorial (still had to figure out how the gui does this, tho). The bottom row is me reverse engineering how to do this with #icestudio blocks.

#opensource #icestudio #fpga #guis #nandland #goboard #babyfpga

David R :antiverified: · @davidr

188 followers · 1385 posts · Server hachyderm.ioAt this moment, am jumping between these tasks

1. creating posters from maps

2. uploading map images to a printing service

3. #fpga tutorial video

4. #icestudio software

5. #python code for #catvideofeed

6. mechanics of #catvideofeed

7. lunch

Not sure why I didn't suspect #adhd before this...

#fpga #icestudio #python #catvideofeed #adhd

David R :antiverified: · @davidr

180 followers · 1341 posts · Server hachyderm.io#icestudio has all the #nandland #goboard #fpga tutorial projects built into it, so I assume that means it is capable enough for this. That's great!

I feel like I'm learning #icestudio instead of #verilog or #vhdl, tho.

It's all open source, so probably the "raw" files it produces aren't going to be hidden from me. I'll just see if I can following a verilog tutorial to make an icestudio project...

#icestudio #nandland #goboard #fpga #verilog #vhdl

David R :antiverified: · @davidr

180 followers · 1338 posts · Server hachyderm.ioI'm really hoping that that the open source #icestudio is half as functional as it is beautiful, because their download Just Ran. #fpga. I have a feeling it's not going to be, tho...

Obijuan · @Obijuan

53 followers · 7 posts · Server mstdn.socialMe acaba de llegar este libro. Quiero aprender más sobre aritmética en punto fijo para implementarlo en bloques de #icestudio para La #FPGA #FPGAwars