philpem · @philpem

545 followers · 3128 posts · Server digipres.clubI had a ponder on my lunch break - what is the Plessey MJ2841 64x4 FIFO in the #JerroldMVP scrambler for? It's wired to the Timing Controller FPGA.

The theory of operation gives a tantalising clue: "scene detection is done by correlation".

This patent fills in the gaps: https://patents.google.com/patent/US4353088A

It's by Oak Communications but was later reassigned to General Instrument. Interestingly it's by Ir. Pieter den Toonder, the founder of Irdeto.

#analogcable

philpem · @philpem

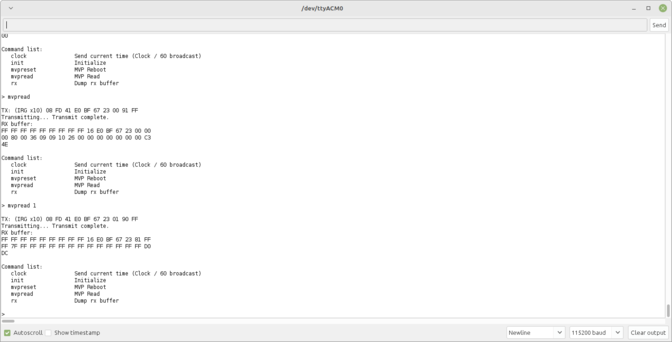

528 followers · 2555 posts · Server digipres.clubMore #analogcable #JerroldMVP work tonight. Starting by getting an Arduino to send commands to it.

philpem · @philpem

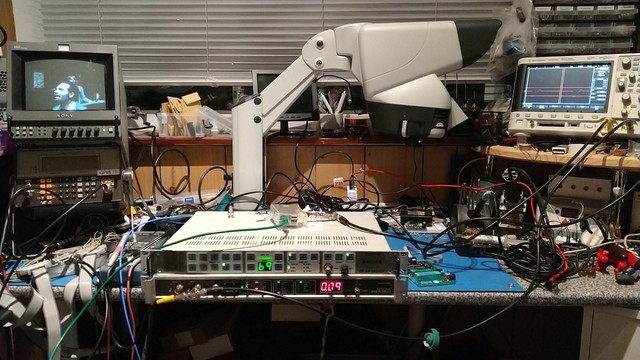

523 followers · 2396 posts · Server digipres.clubFinished off the repairs to the Jerrold MVP scrambler. I'm going to leave the cover off for now, as I'd like to try and figure out the address map, and which switches go to the various tristate buffers.

Hopefully that will make it easier to figure out what the remote control commands do.

#analogcable #JerroldMVP

philpem · @philpem

519 followers · 2174 posts · Server digipres.clubSteadily reverse-engineering the #JerroldMVP #analogcable scrambler. The stack of rack gear doth embiggen.

So far I've learned the line-18 carousel contains eight packets. Segmented Memory on the MSO-X once again proved its worth - by grabbing what seems to be the whole line-18 carousel.

Now I just need to find a way to decode the saved waveforms back into binary data.