screwtape · @screwtape

356 followers · 5572 posts · Server mastodon.sdf.orgSigasi · @Sigasi

1 followers · 1 posts · Server noc.social👋 Hi, we’re Sigasi!

Our #Eclipse and #VSCode based #IDE helps #DigitalElectronics design & #Verification engineers deliver formally validated designs faster and more efficiently with instant code insights, intelligent completions, easy design navigation, zero-noise linting & refactoring.

Want to know more? Ask us anything!

#vunit #uvm #verilog #systemverilog #vhdl #hdl #verification #digitalelectronics #ide #vscode #Eclipse

Abraxas3d W5NYV · @abraxas3d

737 followers · 1498 posts · Server mastodon.radioMore coming for the open source #VHDL #COBS decoder repository from @OpenResearchIns

Very useful for both #satellite and #terrestrial #digital #communications. All #opensource.

There's a script that creates the stimulus files and we'll add a Vivado tcl script that can recreate the project for you.

Thank you to everyone that supports work at ORI! You make it easy to do ambitious things.

#opensource #communications #digital #terrestrial #satellite #cobs #vhdl

Dustin · @DigitalKrampus

48 followers · 625 posts · Server geekdom.socialI was wondering why some logic wasn’t working right in the lab.

I added some recovery handling logic and then forgot to hookup the generic so that particular block was decoding on a completely different bit stack up than the rest of the logic 🤦🏻♂️

And the error was showing up in sim, not sure why I didn’t notice it last week.

🇺🇦🇪🇺 cweickhmann · @cweickhmann

159 followers · 3265 posts · Server qoto.orgInteresting details of ieee.fixed_pkg

Today I learned that in order to assign a negative sfixed (signed fixed-point) signal or variable to another signal or variable, I have to use resize.

process

variable x0: sfixed(7 downto -8) := to_sfixed(1, 7, -8);

constant val: sfixed(7 downto -8) := to_sfixed(10, 7, -8);

begin

-- does not work:

x0 := -val;

https://bowfinger.de/blog/2023/05/interesting-details-of-ieee-fixed_pkg/

Dustin · @DigitalKrampus

34 followers · 375 posts · Server geekdom.socialNothing like have a generic name collision. It would be one thing if the generics had inverse effects across the catalog of logic. It's something else if the generics have different types. I'm not sure which is worse.

PSA: #Xilinx sometimes uses SIM_MODE in their IP. It is not recommended to use the same generic in one's own #VHDL.

PS PSA: when defining a generic in #VHDL, it is best to use std_logic, bit, or std_logic_vector to support VHDL<->SystemVerilog interaction.

PipelineC · @pipelinec

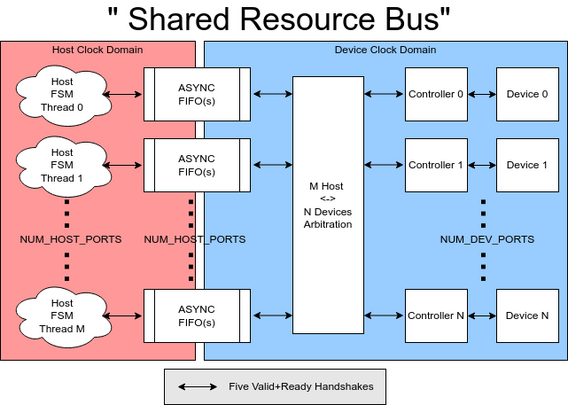

75 followers · 36 posts · Server fosstodon.orgPipelineC's new 'shared resource buses' are pretty neat: Multiple 'threads' of C function derived state machines can easily share resources (memory, compute, etc) by generating AXI-like buses and arbitration. This is still highly experimental but very powerful - reach out if you want to make something together! https://github.com/JulianKemmerer/PipelineC/wiki/Shared-Resource-Bus #rtl #hdl #hls #vhdl #verilog #asic #hardware #multithreaded #hpc

#rtl #hdl #HLS #vhdl #verilog #asic #hardware #multithreaded #hpc

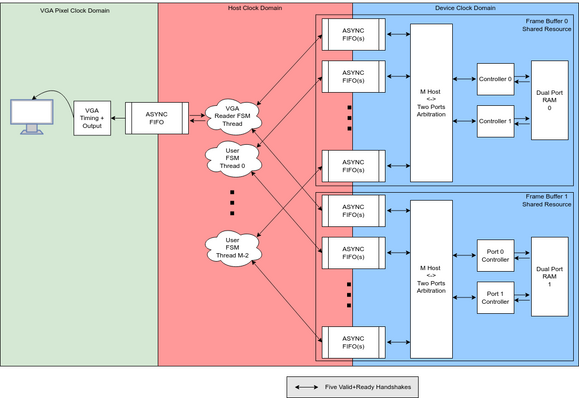

PipelineC · @pipelinec

75 followers · 35 posts · Server fosstodon.orgFrame buffers are the "shared resource" in the recent Game of Life demo. PipelineC generates arbitration between multiple state machine 'threads' simultaneously reading+writing the buffers. What can you do with C code and a frame buffer? https://github.com/JulianKemmerer/PipelineC/wiki/Shared-Resource-Bus#graphics-demo #rtl #hdl #hls #vhdl #verilog #asic #hardware #multithreaded #hpc #computergraphics

#rtl #hdl #HLS #vhdl #verilog #asic #hardware #multithreaded #hpc #computergraphics

PipelineC · @pipelinec

75 followers · 34 posts · Server fosstodon.org'C code' Game of Life in #FPGA at 48FPS 🤓 PipelineC derived state machines and new shared resource buses make it super easy to adapt multi-threaded software C implementations for quick FPGA prototypes. Highly experimental but very powerful - reach out if you want to make something together! https://github.com/JulianKemmerer/PipelineC/wiki/Shared-Resource-Bus#game-of-life-demo

#rtl #hdl #hls #vhdl #verilog #asic #hardware #multithreaded #hpc #computergraphics

#fpga #rtl #hdl #HLS #vhdl #verilog #asic #hardware #multithreaded #hpc #computergraphics

Remi · @remi

65 followers · 663 posts · Server universeodon.comRemi · @remi

65 followers · 658 posts · Server universeodon.comWell appears as if there's no concept of time in #gnuradio. Everything is sample based. It's understandable but means the first helper module I think I will need to write is a sample counter though to provide other modules with a concept of time.

#gnuradio #fpga #aldec #vhdl #riviera

Dustin · @DigitalKrampus

34 followers · 372 posts · Server geekdom.socialMapping #Xilinx stacked AXI4 busses onto indexed records is making me go cross-eyed.

I'm instantiating the AXI4 Crossbar IP, but instead of individual buses for each initiator, it stacks all the bits for every initiator into a single-named port. Ex:

wdata(255 downto 0) -- Initiator 0

wdata(511 downto 256) -- Initiator 1

and ALL of the AXI4 signals are stacked like this.

So I'm writing a wrapper to put them into their own unique records.

Remi · @remi

65 followers · 654 posts · Server universeodon.comAhh the joys of having contributed. I have a package for #VHDL for #SublimeText that I wrote years ago. It mimicked many of the #Emacs vhdl-mode abilities. It was fairly well received (11k users last I checked).

I haven't used Sublime for a while having moved back to Emacs, but still there's pull requests from time to time and then I have to remind myself of how it all works.

Also the joys of trying to lex a language like VHDL. The last issue:

The `is` in the `block` statement is technically optional, however `block` has parenthetical guard statements that come between `block` and `is`. Then after `is` there is a declarative set of statements and then `begin` starts the body region. So while optional I still need `is` as a delimeter between guard statements and declarative statements!

Remi · @remi

65 followers · 654 posts · Server universeodon.com@Tathar Well, for avionics test, I do signal receipt and correlation and demodulation, then the other side modulation and transmission in #VHDL. However that's not what's making me walk through gnuradio. Apparently #Aldec has a block that lets you use #gnuradio in co-simulation with #Riviera-PRO. If I have an easier to work with signal generation or signal analysis tool, it would aid verification.

I've written signal toolbox stuff in VHDL for simulation, but I'll be honest, it's a pain in the ass to work with: tedious to construct and a pain in the ass to modify (depending on what you want.). There's a possibility gnuradio is easier (though also a possibility it is not. I've not yet got through a tutorial that actually gave me a sense of how the tool deals with time. I think it probably doesn't which means if I need a particular timing I will be sample counting and it'll make it anchored to sample rate when it'd just be nicer to wait X microseconds and then modulate.)

#vhdl #aldec #gnuradio #riviera

Remi · @remi

65 followers · 635 posts · Server universeodon.comRemi · @remi

65 followers · 635 posts · Server universeodon.comPlaying around with GNU Radio, a software suite I had no idea existed until the other day. Apparently there's also (when I get more proficient with it) a way to pipe the output of this into Riviera-PRO for FPGA simulation. I have LONG wanted a better signal generation sandbox for verification and this could potentially be very neat. Just a lot of baby steps to learn it, it's a beast of a software and I need to be able to write modulation schemes for SIF, Mode S, et al

#sdr #vhdl #fpga #avionics #aldec #simulation

Am I? · @ami

125 followers · 1089 posts · Server floss.social@meetingcpp

Digit separators are my absolute favorite #modernCpp feature.

There are a lot of reasons to use #Cpp 11+ but having written #VHDL and coming back to not being able to see what number we're talking about (especially if you have a smidgen of #dyscalculia) just feels like such a regression!

#moderncpp #Cpp #vhdl #dyscalculia

Dustin · @DigitalKrampus

27 followers · 311 posts · Server geekdom.socialQuestaSim will fatal at time 0 if a combinatorial term is using a counter to index into a multidimensional array that doesn't start at 0. Probably due to the simulator initializing the index counter as 'X' at time 0, which is then interpreted as 0 in the combinatorial decode.

entity

port(

mdbus : md_type(1 to n);

...

process(clk) begin

if rising_edge(clk) then

if(rst = '1') then

idx <= 1;

else

...

...

some_logic <= '1' when mdbus(idx).foo = '1' else '0';

Remi · @remi

62 followers · 588 posts · Server universeodon.comGot a nice big Tcl script that builds everything for simulation for nearly the whole #fpga project. Probably should have done this a long time ago, but for older projects it wasn't always necessary. Good though to ensure no side effects as the #vhdl blocks grow though. Even have command line arguments for clean and building the core IP blocks too (because really don't want to have to do that every time.)

Not make though. Riviera-Pro doesn't actually build individual object files so there's no way to make targets.

Remi · @remi

62 followers · 581 posts · Server universeodon.comSuper grateful we're starting to see Windows builds of #emacs 29. If only I could get a VHDL DLL for tree-sitter. Not enough of a C-head to know how to build the one repo in Github that has one. (Though to be fair, vhdl-mode already provides first class #VHDL support in Emacs, one reason I use it, so it's not urgent. I'd just like to see what it'll do.)