James against the machine · @j

179 followers · 1472 posts · Server noise.j-w.auIT'S ALL HAPPENING!

Open-source FPGA toolchain on macOS, in my good-friend-and-text-editor, Nova.

I'm still on the hunt for a better way (on a Mac) to synthesize SystemVerilog directly instead of converting it to Verilog first. If YOU know a way, lmkplskthx!

Nova is a fantastic, extensible tool from @cabel and his pals at @panic

#fpga #macDevelopment #yosys #verilog #systemVerilog #tangNano #panicNova #nova

#fpga #macdevelopment #yosys #verilog #systemverilog #tangnano #panicnova #nova

YosysHQ · @yosyshq

434 followers · 39 posts · Server fosstodon.orgyosys users group - meet-up #002

September 7th at 18:00 CEST.

We'll start with a demo of our new formal equivalence checker targetting the #OpenLane #ASIC flow. Bring your own design to follow along!

Afterwards we'll have time for your questions and suggestions.

Feel free to bring a friend!

Use this link to join:

https://meet.jit.si/NoisyAssembliesExpressEach

The YosysHQ team will be present and are looking forward to meeting you!

#openlane #asic #yosys #fpga #meetup

YRabbit · @yrabbit

189 followers · 5306 posts · Server mastodon.sdf.orgComputer Engineering JMU · @ce

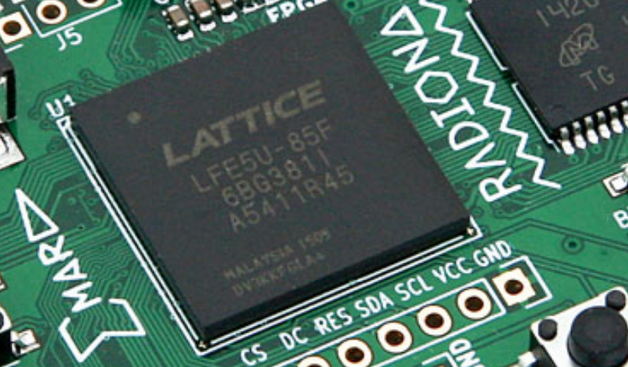

6 followers · 7 posts · Server mastodon.acm.org@phf @yosyshq this is the upduino v1 board with #Lattice #ice40 (there is even a v3) HW Description (mainly a I2C controller) is done in #GHDL and synthesis with #yosys and it’s ghdl plugin. Place and route is done with #nextpnr. Picture shows #FPGA floorplan and utilization.

#lattice #ice40 #ghdl #yosys #nextpnr #fpga

YRabbit · @yrabbit

184 followers · 5147 posts · Server mastodon.sdf.orgThe new PnR architecture for gowin chips has flashing LEDs!

The departure from the old Generic-based architecture was long overdue.

Himbächel - a series of bigger arches

https://github.com/YosysHQ/nextpnr/blob/master/docs/himbaechel.md

Psentee · @psentee

43 followers · 698 posts · Server stolat.townI just wrapped a #nix setup I was using for bleeding edge #yosys / #amaranth toolchain into a reusable flake in case anybody finds it useful: https://gitlab.com/psentee/yoverlay

YRabbit · @yrabbit

175 followers · 4957 posts · Server mastodon.sdf.orgThe hardest part is that I remember that around August 2021 we had already encountered the wrong polarity of the OEN signal and this was solved at the #yosys level.

And it is likely that I will have to take my pants off over my head and ensure the correct polarity and still not affect the yosys.

· @mole99

26 followers · 32 posts · Server fosstodon.org@yrabbit

Very exciting! But please take your time with everything, I will be happy to try it out once it's ready 😃️

By the way, I would be very interested in your thought process and the steps involved in implementing a new primitive like ELVDS in #apicula + #yosys + #nextpnr .

Maybe someday you could toot about this in detail?

RISC-V · @risc_v

707 followers · 2315 posts · Server noc.social.@antmicro adapted the #OpenTitan configuration to fit into a small, accessible @XilinxInc #Artix7 A200T #FPGA, opening the path to synthesizing this #SystemVerilog design with the #opensource #Yosys/UHDM flow. Read more: https://riscv.org/blog/2023/04/adapting-opentitan-for-open-source-fpga-prototyping-and-tooling-development/ @google @chipsalliance

Original tweet : https://twitter.com/risc_v/status/1646134831858819072

#yosys #opensource #systemverilog #fpga #artix7 #opentitan

YRabbit · @yrabbit

168 followers · 4867 posts · Server mastodon.sdf.orgYRabbit · @yrabbit

167 followers · 4864 posts · Server mastodon.sdf.orgOSER16

Generating chip bases, going through #yosys synthesis and #nextpnr placing/rooting😀

Of course, the funniest thing isn't there yet - bit filling - and nothing works. And also about a gazillion correctness checks are missing, but it's a start!

#fpga #apicula #gowin #sipeed

#yosys #nextpnr #fpga #apicula #GoWin #sipeed

xq · @ikskuh

69 followers · 65 posts · Server layer8.spaceTheZoq2 · @thezoq2

62 followers · 153 posts · Server mastodon.social· @talpa

14 followers · 203 posts · Server fosstodon.orgWhen you serial port occasionally reads a byte shifted by one bit. Maybe stop looking for a bug in the serial port logic code and maybe just maybe look at the warning that the 16MHz clock was only able to be generated as 15.6MHz...

You know that warning that you brushed off as that's probably close enough, and recalculate baud rate divider for the actual clock instead.

TheZoq2 · @thezoq2

61 followers · 144 posts · Server mastodon.socialAlways amazing to see how much synthesis tools are able to optimize. Today #yosys managed to infer that because I only read every 4 instructions in my program ROM, the end marker it was looking for would never be found. It therefore just completely optimized away the CPU, because it would never get the start signal 👀

· @talpa

14 followers · 176 posts · Server fosstodon.orgSurprisingly how enjoyable it is to write a serial port (for the second time) in #verilog.

This time intended to be synchronous to the "sysclk".

It sure makes it easier to stick with just one clock domain :)

And yes I know that this will probably be the millionth time any one has written an uart.

Also if you like FPGAs go checkout #yosys and #nextpnr they are amazing projects

· @talpa

13 followers · 171 posts · Server fosstodon.orgAlso incredible how much better they feel than the closed source programs (granted I have only tried Xilinx, but holly GB-atman that is a large software package, also sure is annoying to renew there stupid license)

YRabbit · @yrabbit

148 followers · 4547 posts · Server mastodon.sdf.orgIt has just come to my attention that the vendor IDE has a VGA example as part of it.

So I just took it and compiled #yosys->#nextpnr->#apicula

And marvel: no difference! The example uses PLL and it's the same source code! (well, except for two unimportant lines, and it's not my fault - I know exactly how to code these ports, but I need to change #yosys)

#fpga

#yosys #nextpnr #apicula #fpga

Benoît Allard · @benallard

5 followers · 11 posts · Server osna.socialThere is this game #TuringTumble, it’s about solving logic #puzzles in a very tactile way: literally with balls and switches. Well, it‘s first about #synthesising, and then #place-n-routing the pieces on the board. See where I’m aiming at? We do actually have tools that do that very well! What‘s needed is *just* defining our board and it’s components in a formal way to be compatible with #yosys and #nextpnr. Then we will be able to express any #verilog as a Turing-tumble board. Yeah!

#TuringTumble #puzzles #synthesising #place #yosys #nextpnr #verilog

antifuse · @antifuse

166 followers · 17 posts · Server infosec.exchangeI pretty much never use VS Code, as I mostly live in Jetbrains products and #neovim..but I have to say using it for #verilog design has been a surprising pleasure. Through various plugins I can design with language server support, run test benches, view VCD waveforms, and even synthesize circuits with #yosys to produce visual diagrams.